Figure 1991a shows the schematic diagram of 3D NAND flash memory array with multi-layer bitline and string select line connections:

- SSL (String Select Line):

- Island-gate SSL: Indicates the string select line that connects different layers of the memory cells.

- Multiple SSLs (SSL0, SSL1, ..., SSL7) are shown, corresponding to different layers and connections within the memory array.

- ML1: For SSL local interconnect.

- Indicates a local interconnect for string select lines, possibly for signal routing within a local section of the memory array.

- 64-WL (Word Line):

- Shows that 64 word lines are connected to the WL decoder, controlling the gates of the memory cells.

- The word lines are repeated in the X direction for various units, indicating a large array of memory cells.

- GSL (Ground Select Line):

- Connected to the source line (poly trench) at the bottom.

- Used to select the ground connection for the memory strings during operations.

| Figure 1991a. Schematic diagram of 3D NAND flash memory array with multi-layer bitline and string select line connections. [1] |

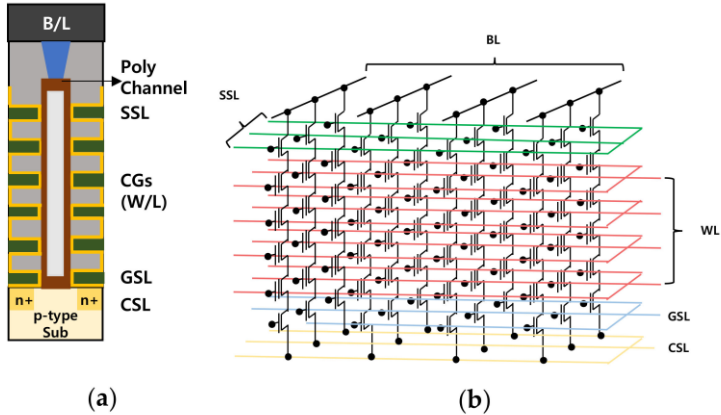

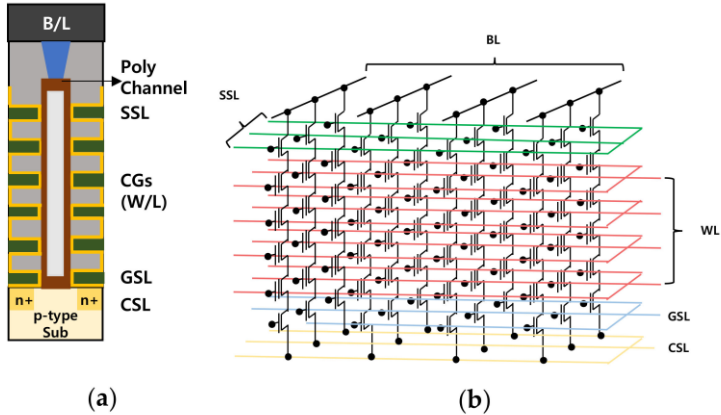

Figure 1991b. Schematic diagram of 3D NAND flash memory array. [1] |

Figure 1991c. 3D NAND flash memory array. [2] |

Figures 1991d shows cross-section view and equivalent circuit diagram of 3D NAND flash array structure.

| Figures 1991d. .(a) Cross-section view and (b) equivalent circuit diagram of 3D NAND flash array structure. [3] |

[1] Kuo-Pin Chang, H. Lue, etc., Memory Architecture of 3D Vertical Gate (3DVG) NAND Flash Using Plural Island-Gate SSL Decoding Method and Study of it's Program Inhibit Characteristics, 4th IEEE International Memory… 20 May 2012, Computer Science Engineering, 2012 4th IEEE International Memory Workshop, DOI:10.1109/IMW.2012.6213641Corpus.

[2] https://www.eetimes.com/first-look-at-samsungs-48l-3d-v-nand-flash/2/.

[3] Geun Ho Lee, Sungmin Hwang, Junsu Yu and Hyungjin Kim, Architecture and Process Integration Overview of 3D NAND Flash Technologies, Appl. Sci. 2021, 11, 6703. https://doi.org/10.3390/app11156703.

|