SECDED (SEC with Double Error Detection) - Integrated Circuits and Materials - - An Online Book - |

||||||||

| Integrated Circuits and Materials http://www.globalsino.com/ICsAndMaterials/ | ||||||||

| Chapter/Index: Introduction | A | B | C | D | E | F | G | H | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z | Appendix | ||||||||

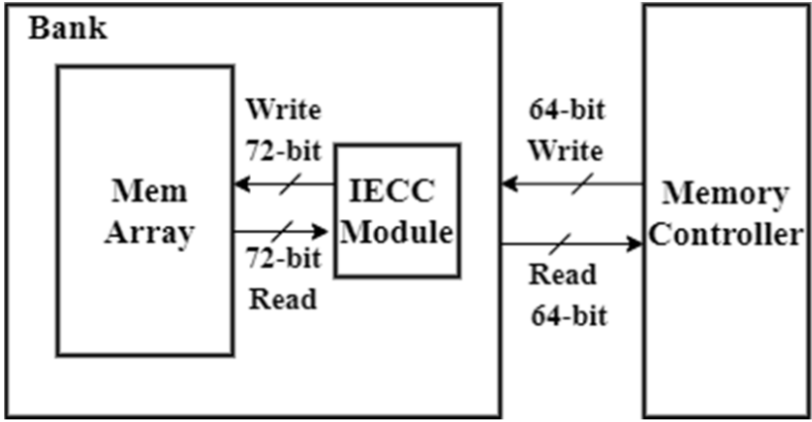

================================================================================= Figure 2220a shows an architecture of a DRAM bank with a (72, 64) In-DRAM ECC (IECC) module. When the memory controller issues a write command of a 64-bit data, the IECC module writes a 72-bit data by adding a generated 8-bit parity to the memory array. This data plus the parity bit is called codeword. In case of a read operation, the IECC module reads a 72-bit data, and checks and corrects the error before sending a 64-bit data to the memory controller. [1] There are two types of Hamming codes that are commonly used as IECC:

Figure 2220a. DRAM bank with IECC module. [3] ============================================

[1] Jeong, Sangmok, SeungYup Kang, and Joon-Sung Yang. "PAIR: Pin-aligned In-DRAM ECC architecture using expandability of Reed-Solomon code." 2020 57th ACM/IEEE Design Automation Conference (DAC). IEEE, 2020.

|

||||||||

| ================================================================================= | ||||||||

|

|

||||||||