Subthreshold Swing (SW) - Integrated Circuits and Materials - - An Online Book - |

||||||||

| Integrated Circuits and Materials http://www.globalsino.com/ICsAndMaterials/ | ||||||||

| Chapter/Index: Introduction | A | B | C | D | E | F | G | H | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z | Appendix | ||||||||

================================================================================= Subthreshold leakage (ISubVth) S-RCAT (Sphere-shaped-Recess-Channel-Array Transistor) technology is a modified structure of the RCAT (Recess-Channel-Array Transistor) and shows an excellent scalability of

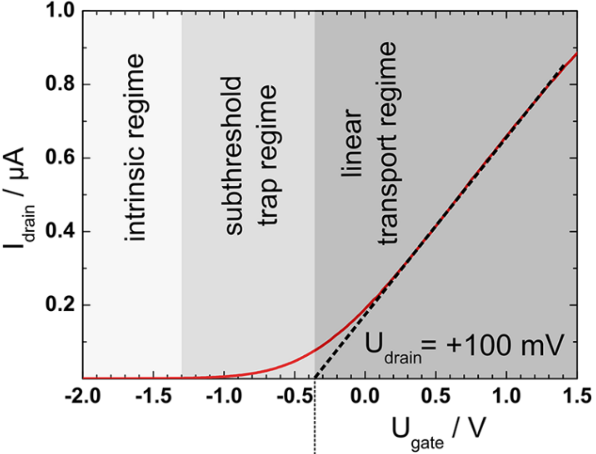

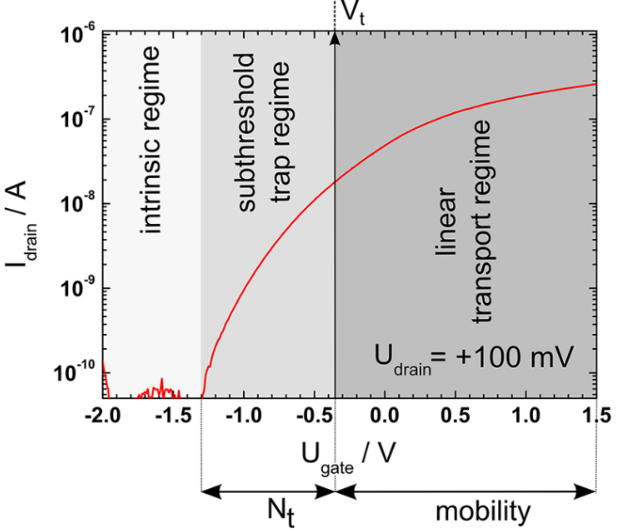

recessed-channel structure to sub-50 nm feature size. [1] Comparing to the RCAT structure, the S-RCAT demonstrated superior characteristics in: In general, the preconductive subthreshold regime is on the order of a few hunded millielectronvolts. Figure 2411 shows the intrinsic, subthreshold, and conducting regimes of a FET. The subthreshold regime is characterized

by a sharp increase in the log(Idrain) versus Vg plot. The subthreshold

swing, S, is defined as the increase in gate voltage per

10-fold increase in source-drain current, in the range

of 250 - 450 mV decade-1. The subthreshold swing, S, can be used to estimate the two-dimensional trap density within the active region of quantum dots at the FET interface. [3] The log scale transfer characteristic includes:

For a wiggling active area (fin) in an advanced 1x DRAM process, from the logarithmic Id-Vg curve, it was shown that the fatter fin exhibited much higher off-state leakage and larger subthreshold swing, indicating that channel controllability is weak. The leakage in a fatter fin dramatically increased at higher drain voltages, while it was not so obviously changed in a thinner fin. [2] In theory, for FinFETs, the OFF-current, leakage current, GIDL, and subthreshold swing increase with increasing temperature, whereas the ON-current, low-field mobility, and threshold voltage decrease with temperature. [4] ============================================

[1] J.Y. Kim, H.J. Oh, D.S. Woo, Y.S. Lee, D.H. Kim, S.E.Kim, G.W. Ha, H.J Kim, N.J. Kang, J.M. Park, Y.S. Hwang, D.I. Kim, B.J. Park, M. Huh, B.H. Lee, S.B. Kim,

M.H. Cho, M.Y. Jung, Y.I. Kim, C. Jin, D.W. Shin, M.S. Shim, C.S. Lee*, W.S. Lee*, J.C. Park**, G.Y. Jin, Y.J. Park and Kinam Kim, S-RCAT (Sphere-shaped-Recess-Channel-Array Transistor) Technology for 70nm DRAM feature size and beyond, Digest of Technical Papers. 2005 Symposium on VLSI Technology, DOI: 10.1109/.2005.1469201, 2005.

|

||||||||

| ================================================================================= | ||||||||

|

|

||||||||