Wordline (WL) - Integrated Circuits and Materials - - An Online Book - |

||||||||||||||||||||

| Integrated Circuits and Materials http://www.globalsino.com/ICsAndMaterials/ | ||||||||||||||||||||

| Chapter/Index: Introduction | A | B | C | D | E | F | G | H | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z | Appendix | ||||||||||||||||||||

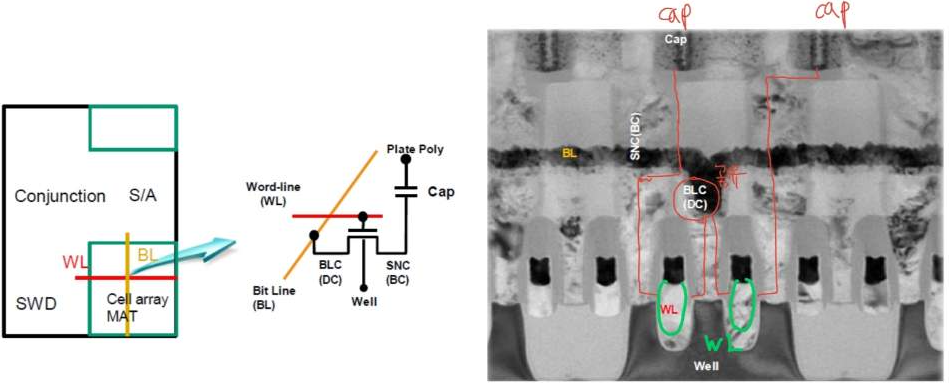

================================================================================= The read process of all memory devices is common. After settling the predefined voltage to the bit line, the bit line is electrically connected with the memory cell. Then, the stored bit information of the cell will modulate the bit line voltage or current. The modulated analog value (voltage or current) of a bit line is then converted to the digital value (namely, GND or VDD) by the sense amplifier (SA) circuit. Since the DRAM cell is a capacitor, the charge sharing process can modulate the bit line voltage as shown in Figure 4890a. [1] Figure 4890a. DRAM and its equivalent circuit models. [1]

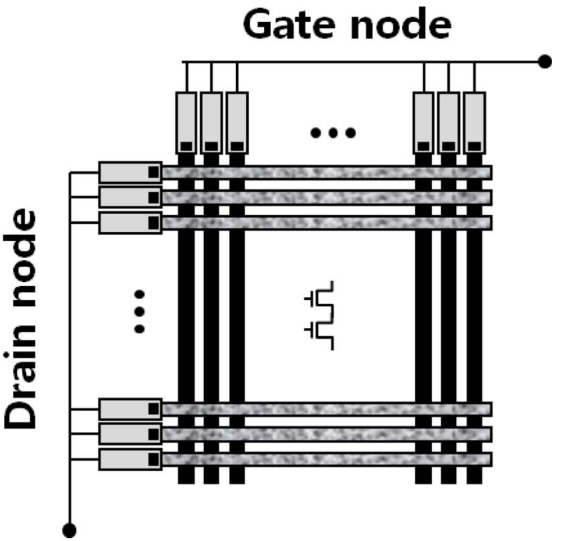

Figure 4890b. Gate (WL) and drain nodes in DRAM. [8]

Figure 4890c. Structure of DRAM and peripheral circuitry. [10] Figure 4890d shows the cross-section view for (a) stacked DRMA cell and (b) trench DRAM cell. Historically, a stacked cell approach [2] was commonly used for commodity DRAMs. However, in this structure, the capacitor over the device is built after the device has been built, which makes it difficult to keep the logic transistor performance. On the other hand,, it is difficult to planarize the surface of the silicon due to the stacked capacitor. Furthermore, if the wiring rule is changed, most logic library elements need to be redeveloped, which can be expensive. This may cause performance degradation due to wiring capacitance and resistance delays. The trench capacitor in Figure 4890d (b) can be fabricated by digging the hole in the silicon before the device has been built. This method will allow for a fully compatible process to logic technology and will not degrade transistor performance, giving an ideal technology solution for embedded DRAM integration in a logic chip. [3]

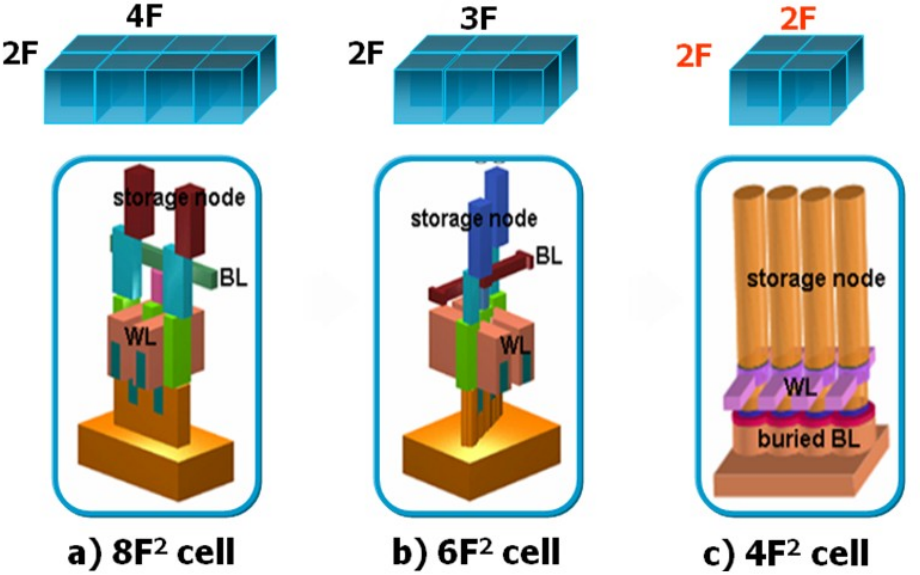

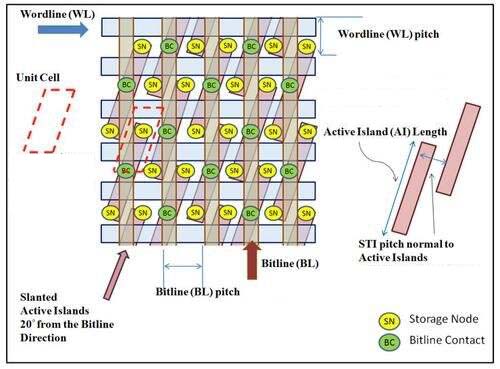

The cell architecture shown in Figure 4890e has been evolved from 8F2 cell to 6F2 cell since the cell size could be reduced up to 75% at the same design rule (F). [9]

Figure 4890f shows DRAM 8F2 cell structure:

Figure 4890f. DRAM 8F2 cell structure. [10]

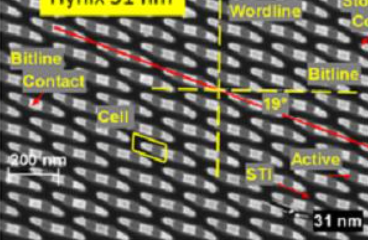

Figure 4890h. Cell Layout of a Samsung DRAM using the buried wordline (bWL). Adapted from [12] Figure 4890i shows a diagram of a basic sense amplifier. More complex sense amplifiers in modern DRAM devices contain the basic elements, as well as additional circuit elements for array isolation, careful balance of the sense amplifier structure, and faster sensing capability. In Figure 4890i, the equalization (EQ) signal line controls the voltage equalization circuit. The functionality of this circuit is to ensure that the voltages on the bitline pairs are as closely matched as possible. Since the differential sense amplifier is designed to amplify the voltage differential between the bitline pairs, thus any voltage imbalance that exists on the bitline pairs prior to the activation of the access transistors would degrade the effectiveness of the sense amplifier. [6] Figure 4890i. Diagram of a basic sense amplifier. [6] 2.39 Mb embedded DRAM (eDRAM) macros [3] shown in Figure 4890j are organized by upper and lower memory units, each consisting of four 299 Kb sub-arrays (0 through 3) and a 16 row redundancy array (R). They are supported by the Input and Output circuitry (IOBLK) located between two memory units. When the macro decoder receives a valid macro-select-signal and a valid read or write command, then the decoder evaluates the address, activating either the top or bottom memory units. The activation of the memory unit enables one of the four arrays, and sends 1 of 256 valid addresses. The 299 Kb sub-array includes ECC bits for IBM servers. An evolutionary approach in this eDRAM locates the segmented WL drivers in the sense amplifier area, which couples to the horizontally arranged WLs through the vertically arranged wires.

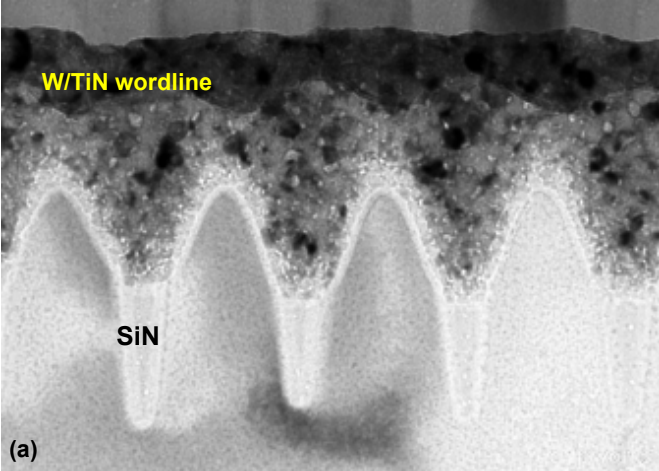

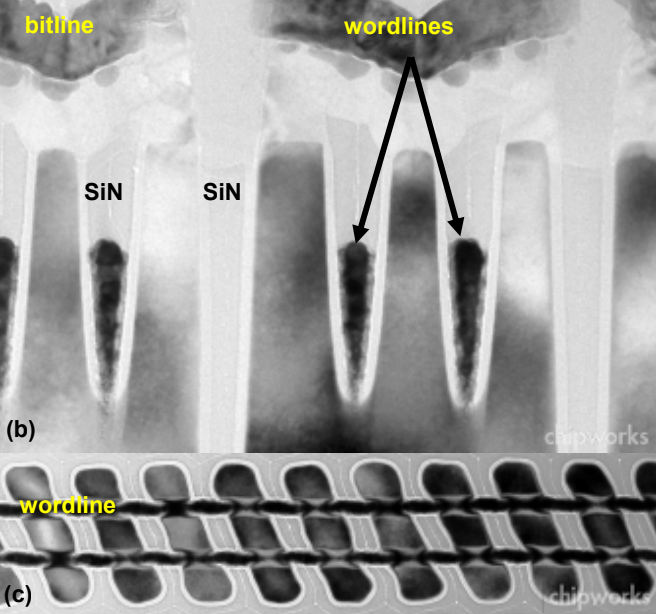

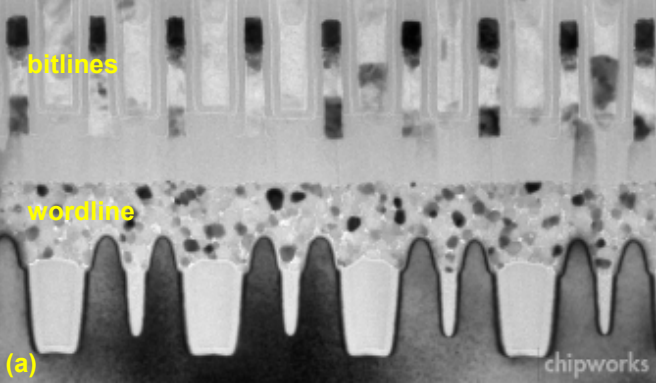

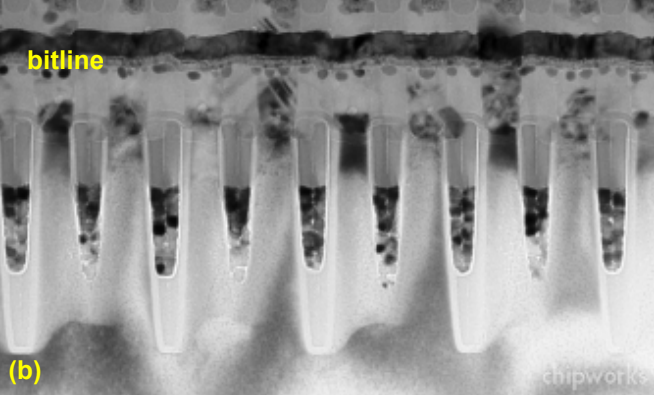

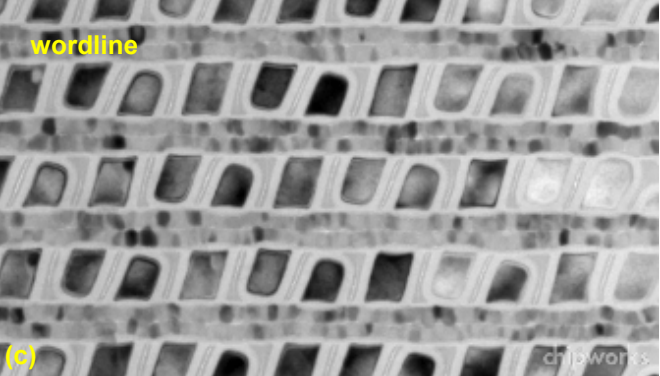

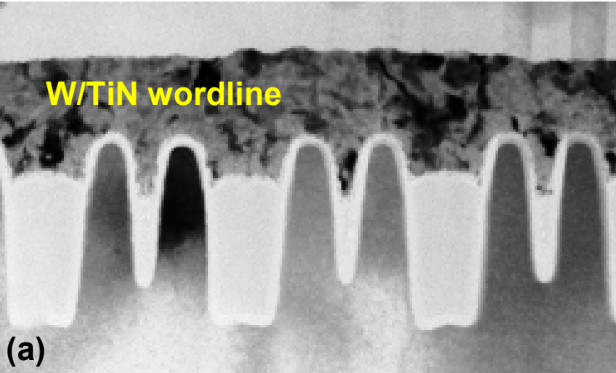

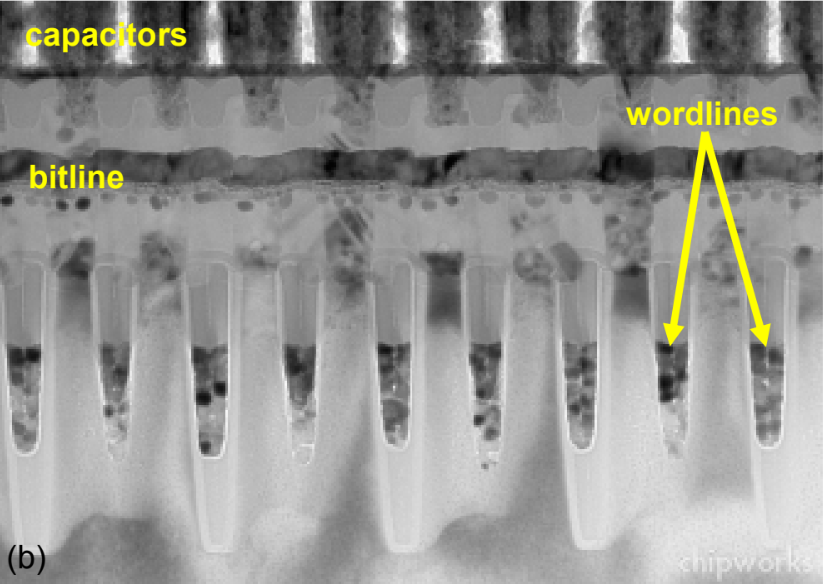

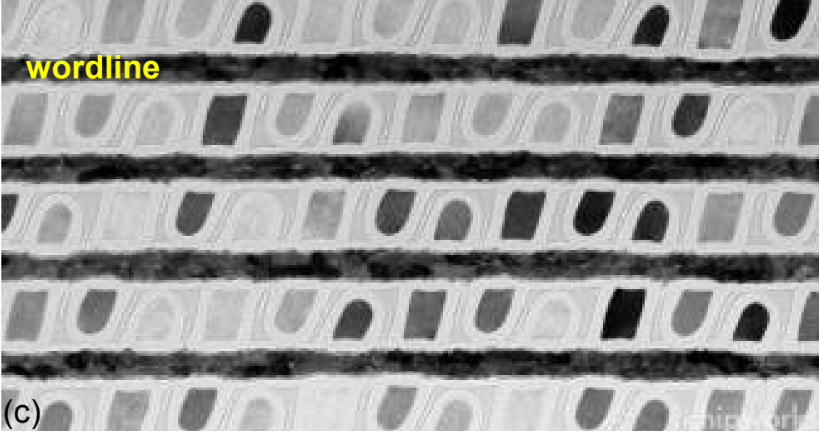

When a voltage is applied voltage on the word line (WL) and the transistor is turned on, the charges are stored in the capacitor through the bit line. At this time, when a high voltage(Vdd) is applied to the bit line (BL), DATA 1 is stored in the capacitor, and when a low voltage (Vss, 0 V) is applied, DATA 0 is stored. Figure 4890k shows the TEM images of W/TiN buried wordlines in Elpida 33-nm DRAM. The "finFET" is wrappied over a tapered channel. However, it is not a true finFET since the channel is unlikely to be fully depleted, and the taper increases the width of the wordline transistor.

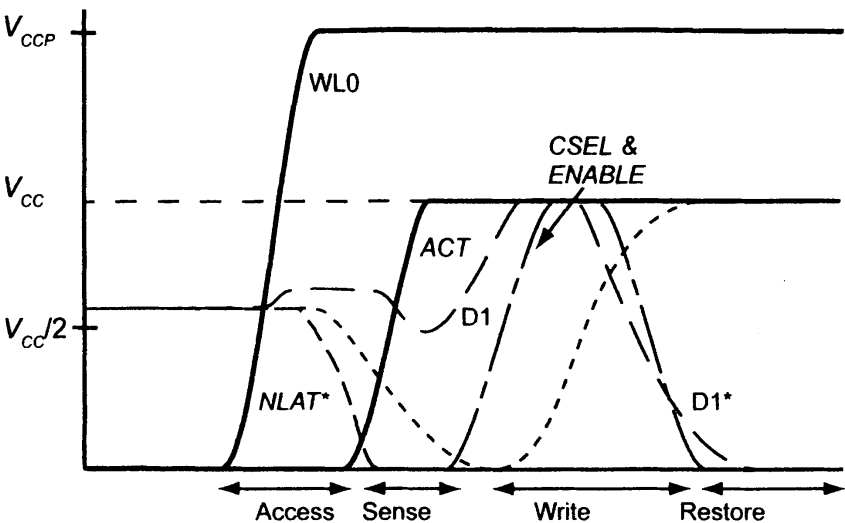

The Write driver simply overdrives the sense amplifiers. Figure 4890n shows the Write operation waveforms in DRAM.

[1] Krzysztof (Kris) Iniewski, CMOS Processors and Memories, (2010).

|

||||||||||||||||||||

| ================================================================================= | ||||||||||||||||||||

|

|

||||||||||||||||||||